CPU UTK

1.Podstawowe elementy CPU

2.Obudowy i gniazda CPU

3.Działanie CPU

4. Bios - nazwy pamięci, składniki, definicja

5. Maigstrale, architektury procesora

|

Pojęcie |

|

1. Układ sterowania CU - Odpowiedzialny za sterowanie blokami mikroprocesora |

|

2. ALU - Odpowiedzialna za wykonywanie przez CPU operacji arytmetyczno – logicznych na l. naturalnych (binarnych) |

|

3. FPU - Wykonuje operacje arytmetyczne na l. zmiennoprzecinkowych (binarnych) |

|

4. Rejestr rozkazów IR - Przechowuje przetwarzaną obecnie instrukcję |

|

5. Licznik rozkazów PC - Przechowuje kolejne adresy pamięci z rozkazami |

|

6. Akumulator - Przechowuje wynik wykonywanej operacji |

|

7. Wskaźnik stosu SP - Służy do adresowania pamięci w trybie LIFO |

|

8. Rejestr flagowy - Przechowuje informacje dotyczące realizacji wykonywanej operacji |

CPU składa się z tranzystorów, które dzieli się na:

- N - negatywne(ładunek ujemny),

- P - pozytywne(naładowne dodatnio),

- bipolarne - sterowane za pomocą natężenia prądu,

- unipolarne - sterowane za pomocą napięcia.

|

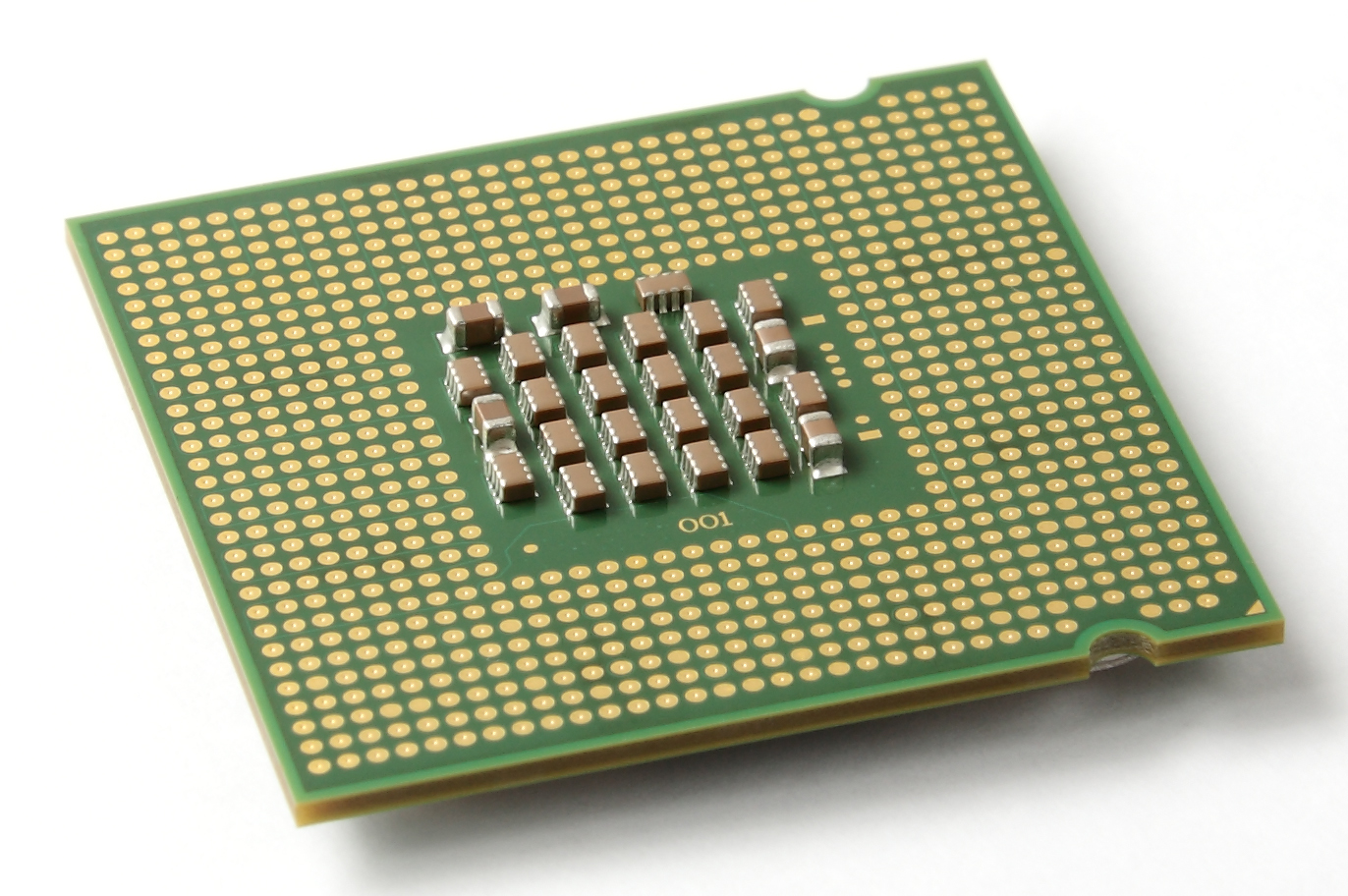

ZDJĘCIE |

NAZWA OBUDOWY + cechy charakterystyczne |

|

|

LGA - pozłacane styki, - brak nóżek |

|

|

SECC - mikroprocesor jest przylutowany do drukowanej płytki - całość jest zamknięta w plastikowej obudowie |

|

|

SEPP - mikroprocesor jest przylutowany do drukowanej płytki |

|

|

CPGA - ceramiczna obudowa rdzenia - nóżki |

|

|

FCBGA - piny zakończone są małymi kulkami |

|

|

PPGA - piny - osłonięty plastikową osłonką |

|

|

SPGA - rozłożenie pinów jest niesymetryczne |

|

Nazwa gniazda CPU |

Zdjęcie |

|

SLOT(SECC, SEPP) |

|

|

SOCKET(PGA) ODMIANY SOCKETÓW: - LIP(trzeba użyć siły 20kg aby go zamontować) - ZIF(posiada klamkę, która dociska mikroprocesor do gniazda) |

|

|

LGA(LGA) |

|

Mikroprocesor współpracuje z pamięcią przechowującą dane oraz sekwencyjne ciągi instrukcji nazwane programem Każda komórka pamięci ma swój adres. Wymiana danych pomiędzy CPU, a pamięcią operacyjną odbywa się za pomocą magistrali pamięci, a adresowanie za pomocąmagistrali adresowej. CPU pobiera z pamięci operacyjnej dane wskazane przez licznik rozkazów PC i umieszcza je w rejestrze rozkazów IR. Układ sterujący PC(pobiera dane z rejestru IR) dekoduje rozkaz oraz ustala argumenty i rodzaj operacji – na tej podstawie przesyłane są dane z rejestru do jednostki ALU, która wykonuje odpowiednie operacje. Po przetworzeniu danych przez arytmometr wyniki umieszczane są w rejestr A lub trafiają do pamięci operacyjnej. Cała procedura odbywa się cyklicznie i w następnych przebiegach przetwarzane są kolejne instrukcje.

BIOS↑w GÓRĘ

Typy pamięci BIOSu:

ROM - programowana przez producenta, nie można było jej edytować.

PROM - była możliwość zaprogramowania tej pamięci jeden raz.

EPROM - wymazywalna i programowalna pamięć. Można było ją wykasować poprzez poddanie działaniu światła ultrapromieniowego.

EEPROM - wymazywalna i programowalna pamięć. Można było ją wykasować poprzez poddanie działaniu prądu o odpowiednim natężeniu i napięciu.

Składniki BIOS:

BIOS setup, BIOST, POST(test systemu), ACPI(interfesj zarządznia enegrią w systemie), Bootstrap loader(miejsce, gdzie są umieszczone pliki rozruchowe).

MAGISTRALE, ARCHITEKTURY↑w GÓRĘ

Magistrala to zestaw ścieżek pozwalająca na połączenie komponemtów między nimi. Chcąc obliczyć ilość pamięci RAM dla danej magistrali, liczbę 2 potęgujemy do liczby linii magistrali.

Typy magistrali:

- równoległa(została wycofana ze względu na występowanie zakłóceń między liniami, używana była w m.in FSB) - działały w trybie HALF-DUPLEX,

- szeregowa(obecnie używana m.in. w USB, SATA, PCI-E) - działa w trybie FULL - DUPLEX.

HALF a FULL DUPLEX

- dupleks (full duplex) - informacje przesyłane są w obu kierunkach jednocześnie, bez spadku transferu, używana w komórkach,

ARCHITEKTURY↑w GÓRĘ

HARWARDZKA(przechowuje dane i rozkazy w jednym bloku pamięci, ale może pobierać dane i rozkazy w jednym bloku pamięci),

MIESZANA(przechowuje dane i rozkazy w oddzielnych blokach pamięci)

CISC(kompleta lista instrukcji)

RISC(zredukowana lista instrukcji)

Pamięc Cache jest zbudowana na bazie pamięci SRAM. Pracuje z pełną prędkością rdzenia CPU. Dzieli się na 3 poziomy:

poziom I - jest zintegrowana z CPU, zawiera kilkadziesiąt kB pamięci SRAM, występuje we wszystkich procesorach od 486,

poziom II - zamonotowana na MOBA poprzez płytkę pracuje z połową prędkośći rdzenia, zamonotowana z rdzeniem pracuje z pełną prędkością rdzenia,

poziom III - stosowany dla CPU serwerowych.

.jpg)